微信小程序是免费的吗seo外链推广

目录

一. 实验目的

二. 实验仪器

三. 实验原理及内容

1.实验原理

2.实验内容

四.实验步骤

五. 实验报告

六. 注意事项

七. 实验过程

1.创建Verilog文件,写代码

编辑

2.波形仿真

3.连接电路图

4.烧录操作

一. 实验目的

- 学会Verilog HDL的case语句应用。

- 学会Verilog HDL的if语句应用。

- 学会使用Verilog HDL进行简单的电路设计。

- 掌握QUARTUSⅡ软件的基本操作和应用。

二. 实验仪器

- PC机一台。

- FPGA实验开发系统一套。

三. 实验原理及内容

1.实验原理

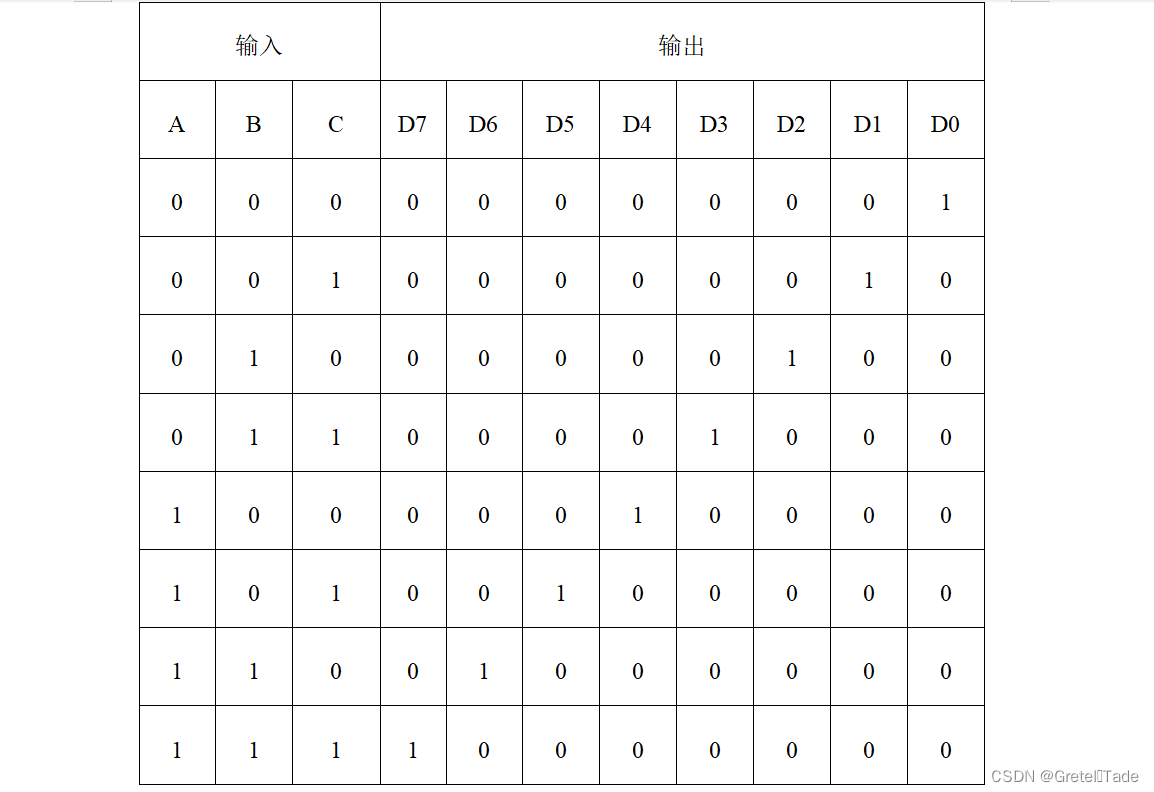

3-8译码器的三输入,八输出。输入信号N用二进制表示,对应的输出信号N输出高电平时表示有信号产生,而其他则为低电平表示无信号产生。其真值表如下所示:

当使能端指示输入信号无效或不用对当前的信号进行译码时,输出端全为高电平,表示任何信号无效。

2.实验内容

用三个拨动开关来表示三八译码器的三个输入(A,B,C),用八个LED来表示三八译码器的八个输出(D0-D7)。通过与实验箱的FPGA接口相连,来验证真值表中的内容。

表3-1 拨动开关与FPGA管脚连接表

| 信号名称 | 对应FPGA管脚名 |

| A | PIN_212 |

| B | PIN_213 |

| C | PIN_95 |

表3-2 LED灯与FPGA管脚连接表

(当FPGA与其对应的接口为低电平时,LED会发亮)

| 信号名称 | 对应FPGA管脚名 |

| LED1 | 167 |

| LED2 | 165 |

| LED3 | 166 |

| LED4 | 162 |

| LED5 | 164 |

| LED6 | 159 |

| LED7 | 161 |

| LED8 | 156 |

| LED_CS | 174 |

四.实验步骤

1.开机,进入QUARTUSⅡ软件系统。

2.建立工程。主芯片为Cyclone2系列EP2C20Q240C8N型号。

3.新建一个Verilog HDL File文件。

4.使用Verilog语言编写3-8译码器。

5.保存文件。

6.将文件设置为工程的顶层文件并编译。

7.创建仿真文件University Program VWF,添加所需的变量并进行功能仿真。

8.分析仿真结果

9.配置管脚

编译综合下载验证。

五. 实验报告

- 总结Verilog设计多路选择器使用的最基本与核心的语法知识。

- 对仿真的结果进行分析。

- 讨论自己在设计过程中遇到的问题、解决的过程以及收获体会。

六. 注意事项

- 在对LED操作时不要忽略LED的使能;

- 8个LED与芯片管教一定要按顺序配置。

七. 实验过程

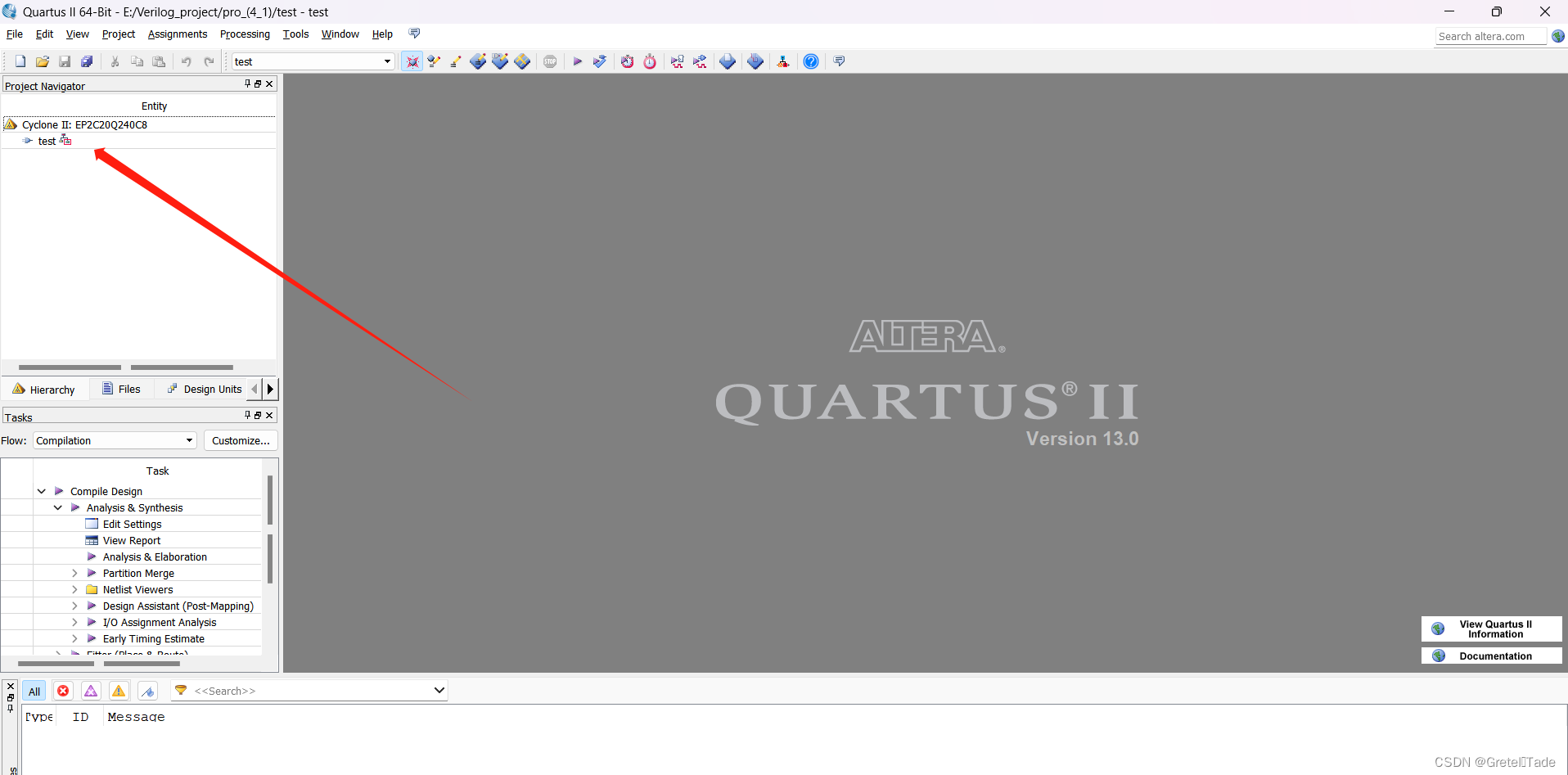

点击New project……创建新工程

然后设置项目的路径和名称(自己设置就好了)

选择相对应的芯片类型(看自己情况选择)

创建完成!

创建完成!

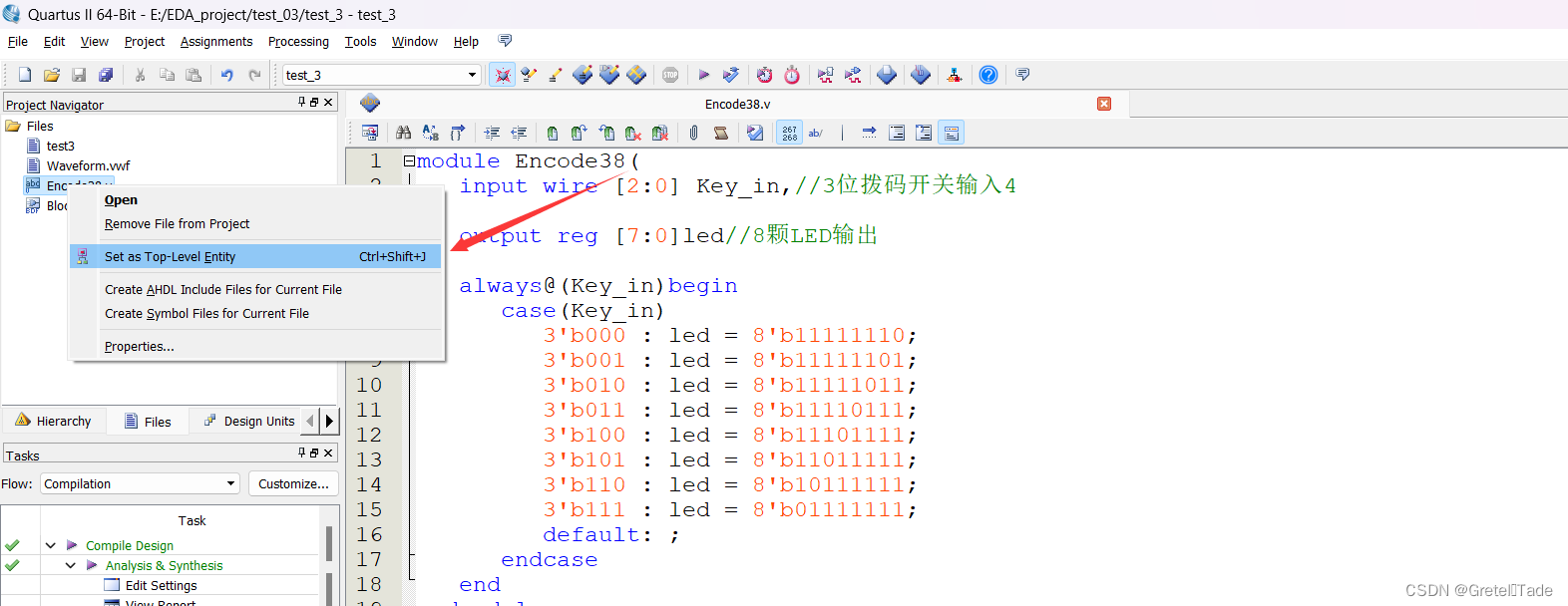

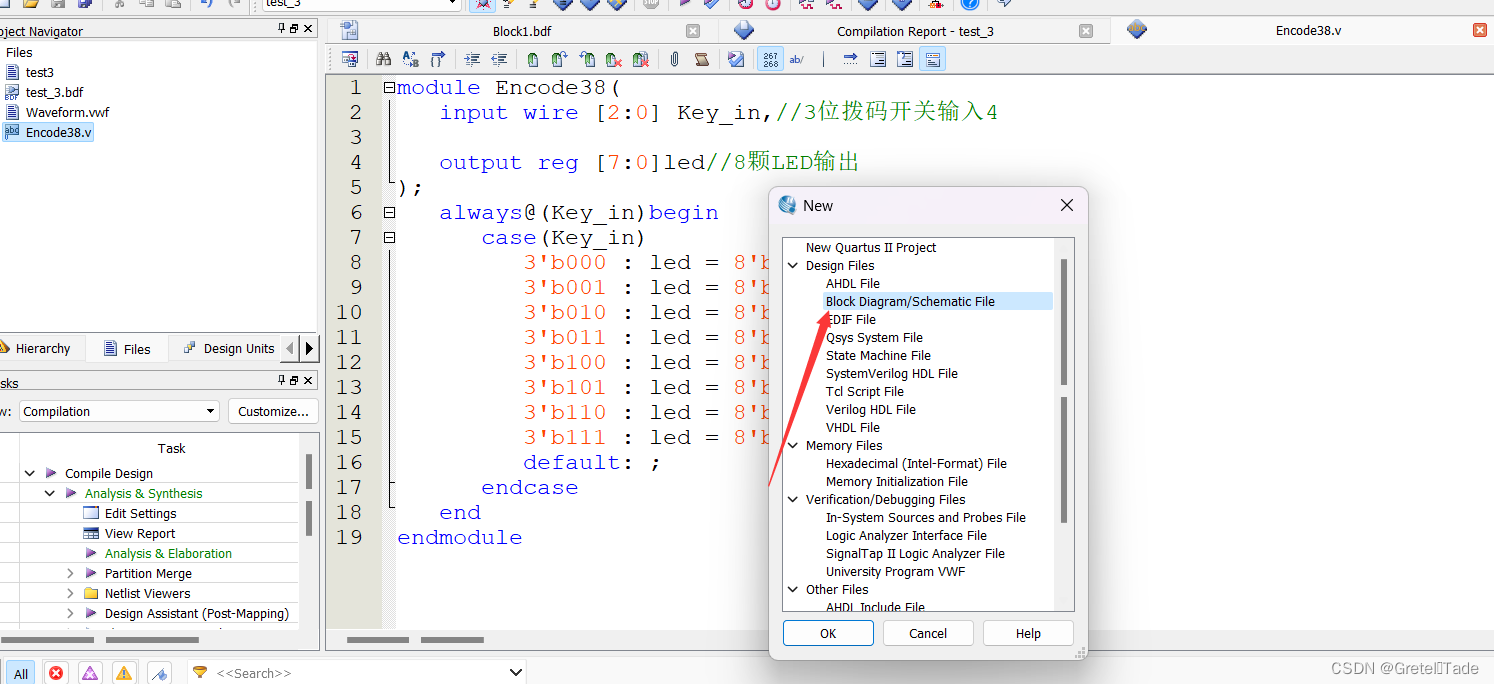

1.创建Verilog文件,写代码

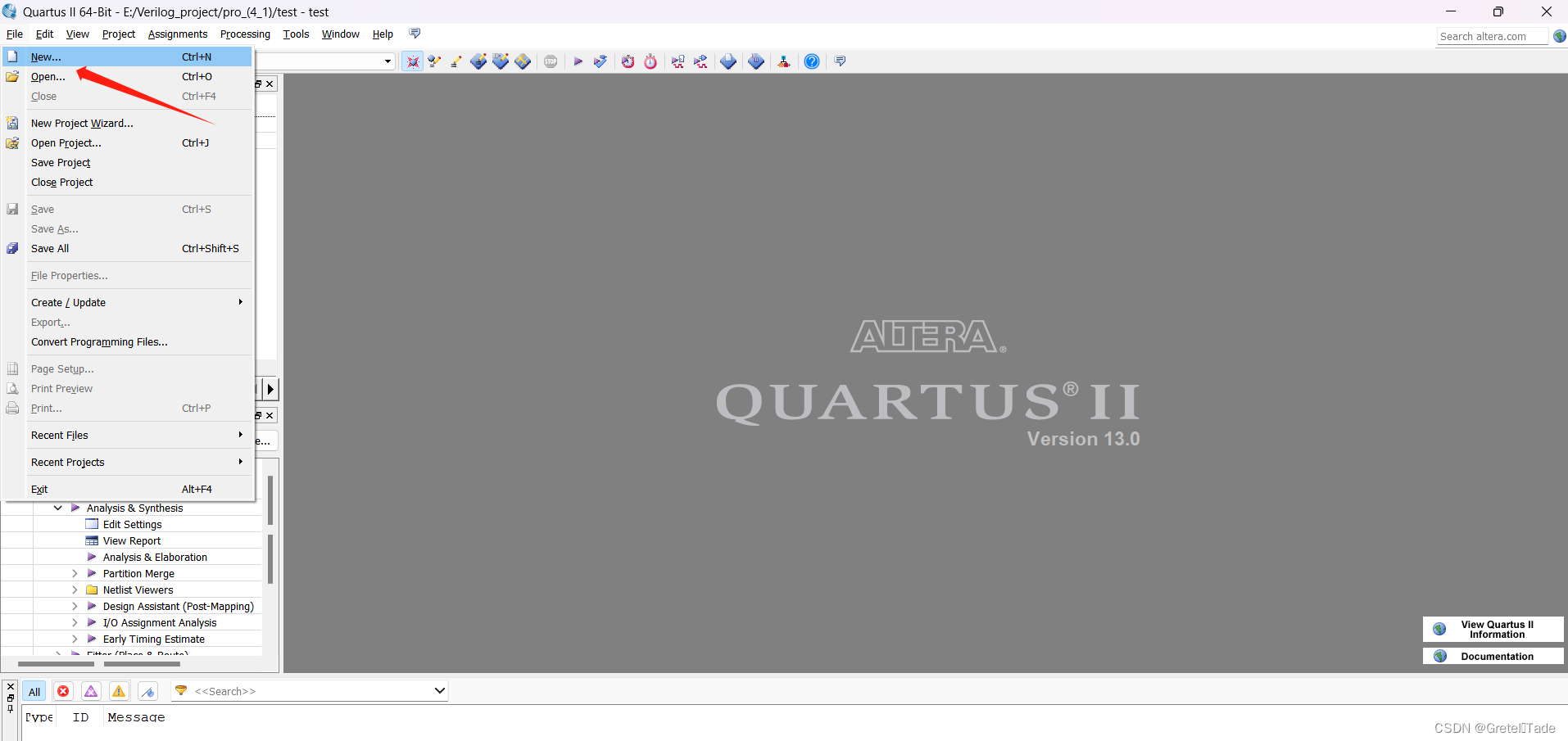

点击New,创建文件

选择Verilog文件,创建

选择Verilog文件,创建

然后就是写代码,写完之后就进行保持文件,把文件的名称跟模块的名称改成一样。(必须一致)

代码如下:

module Encode38(input wire [2:0] Key_in,//3位拨码开关输入4output reg [7:0]led//8颗LED输出

);always@(Key_in)begincase(Key_in) 3'b000 : led = 8'b11111110;3'b001 : led = 8'b11111101;3'b010 : led = 8'b11111011;3'b011 : led = 8'b11110111;3'b100 : led = 8'b11101111;3'b101 : led = 8'b11011111;3'b110 : led = 8'b10111111;3'b111 : led = 8'b01111111;default: ;endcaseend

endmodule 这里我们要把当前Verilog文件设置为顶层文件(也就是主函数的意思),设置好了之后就可以编译运行了。

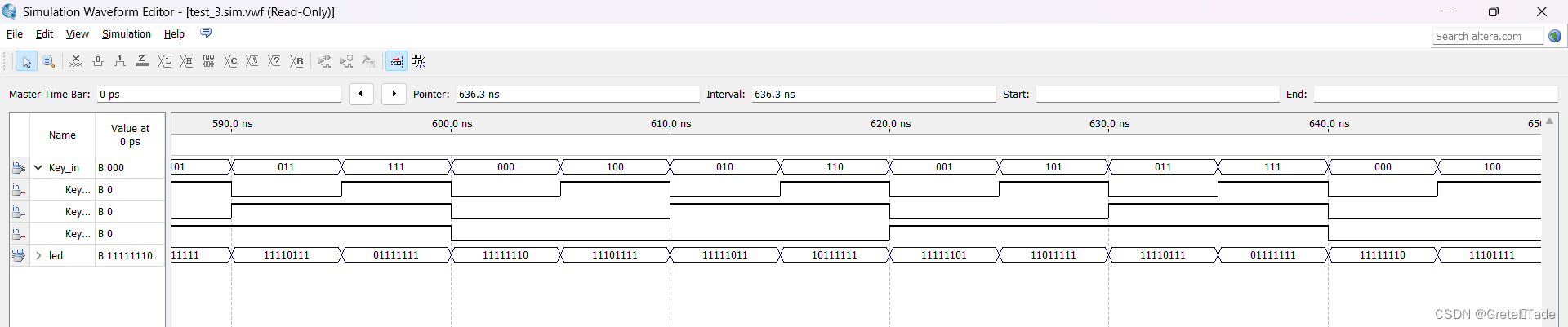

2.波形仿真

设置好仿真界面,仿真结果如下:

然后进行对比,仿真无误后就进行电路图连接。

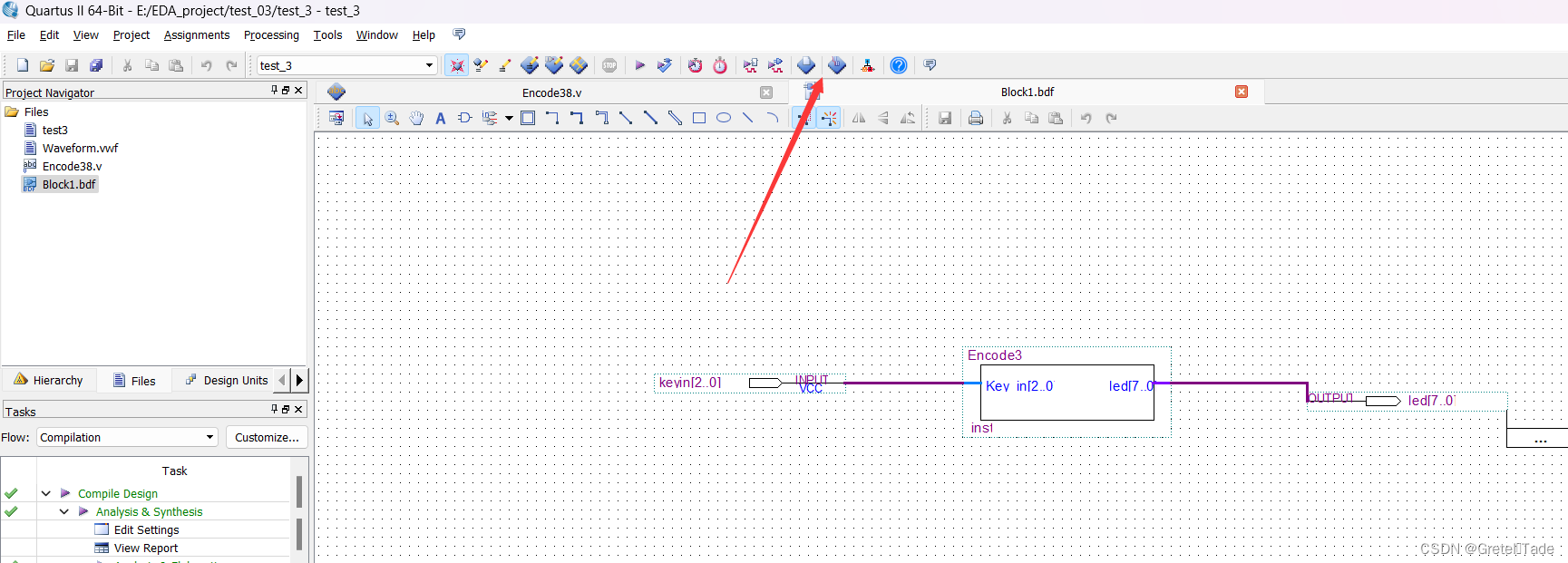

3.连接电路图

点击New,创建block文件,如图所示:

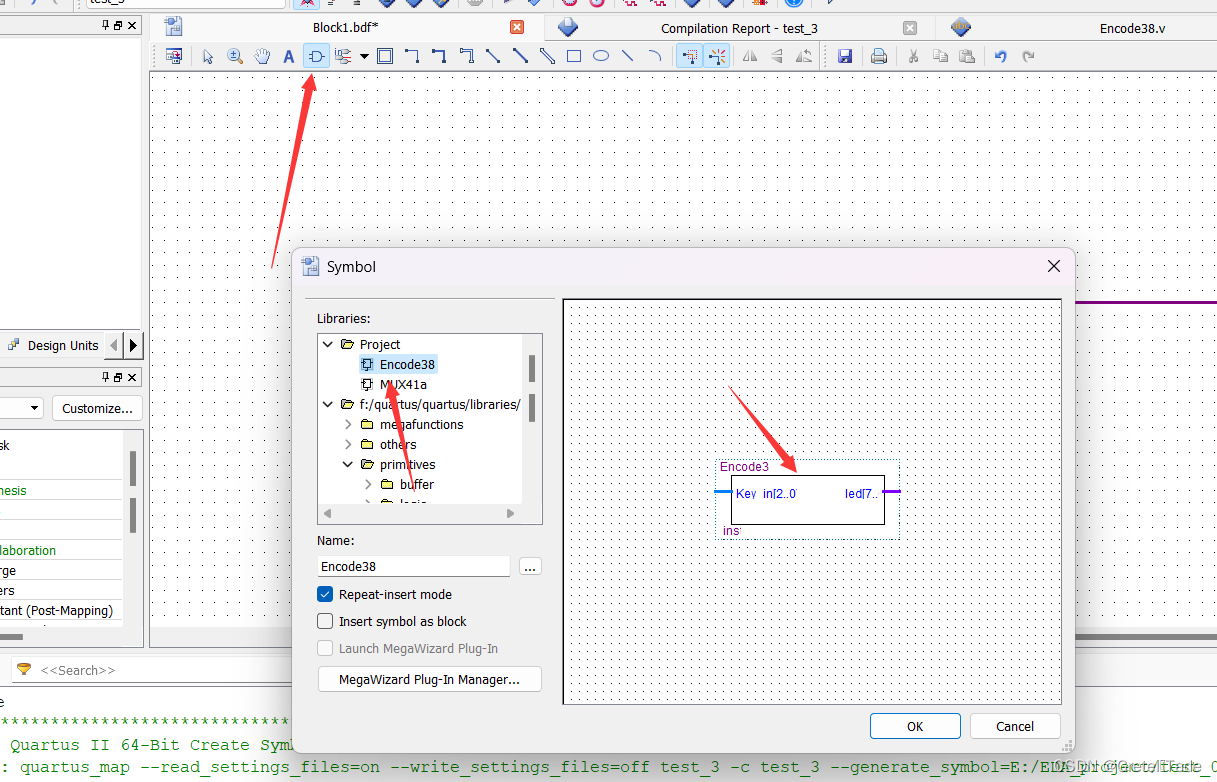

点开file,然后鼠标右键Verilog文件,生成子模块文件。

点开block文件,然后点击元器件查看,这里我们就可以看到project文件夹里面有一个我们用Verilog代码写的元器件,然后就可以进行输入输出连线处理。

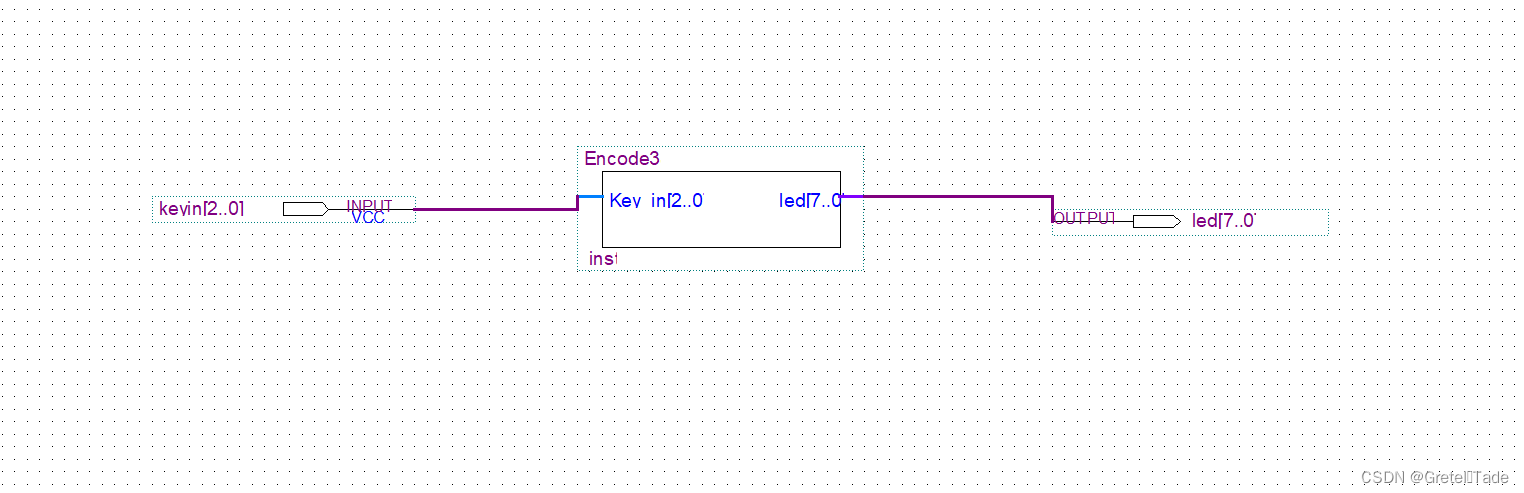

然后就是连线处理 ,结果如下图所示。

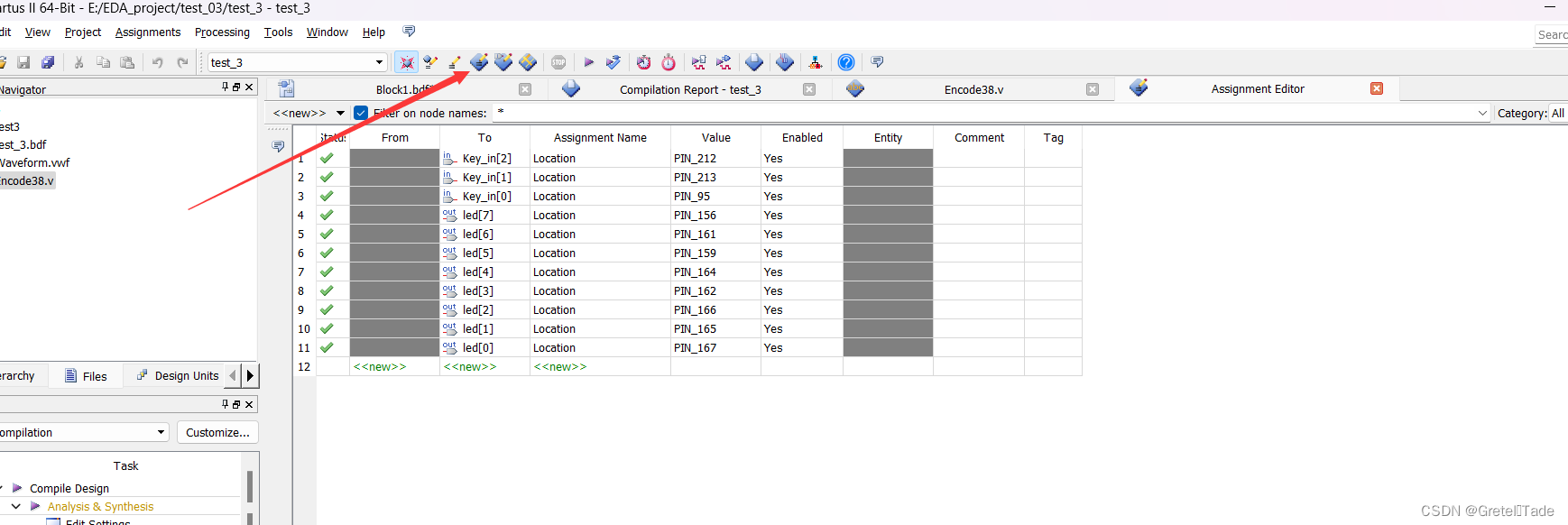

最后连接好元器件之后就进行引脚的绑定,步骤如图所示。

最后连接好元器件之后就进行引脚的绑定,步骤如图所示。

绑定完成之后,我们可以点开这里查看绑定 最后就是编译运行,运行无误。

最后就是编译运行,运行无误。

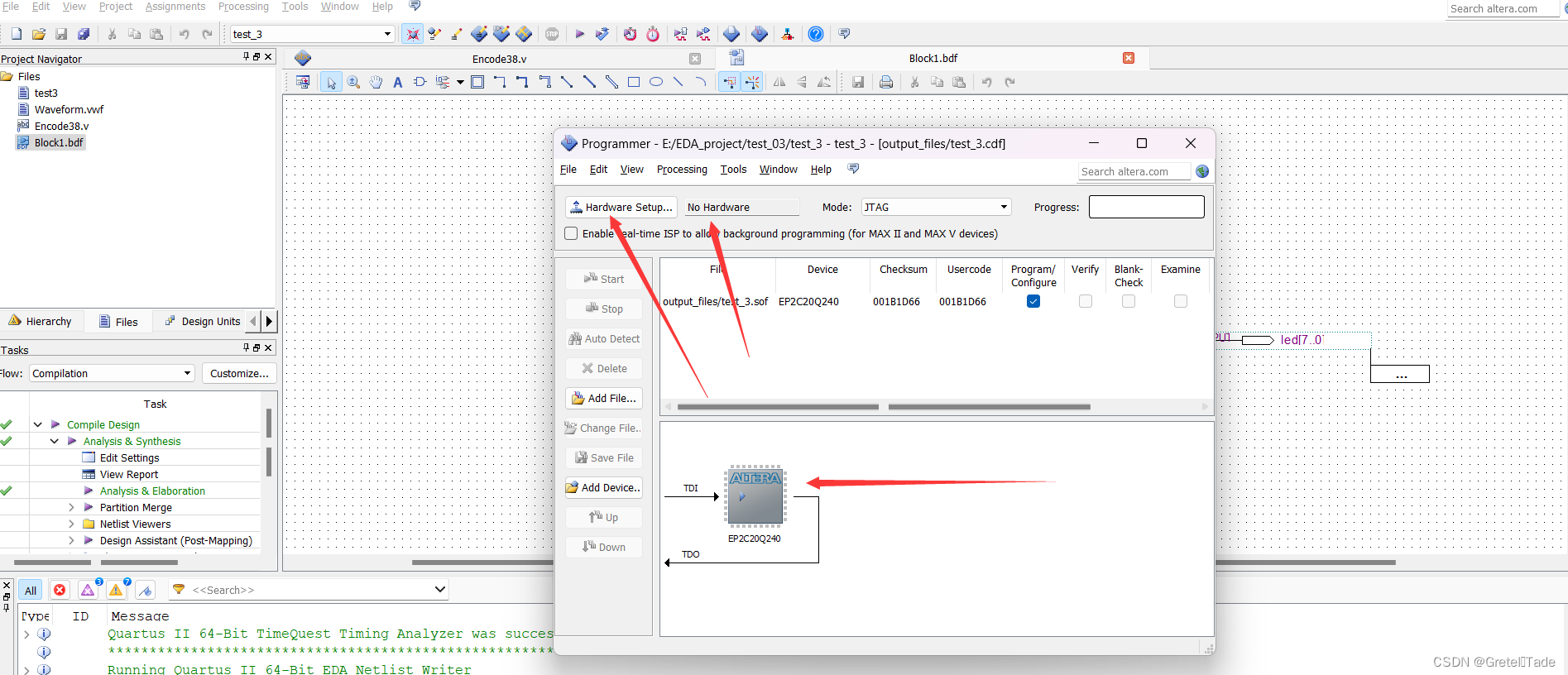

4.烧录操作

点击此处

这里我们就可以看到有一个芯片,也就是我们生成的sof文件,只需要把这个文件烧录到你的开发板就行了。(注意:上面如果显示No Hardware的话,要点开旁边的接口设置,设置为USB接口就行了,连接了开发板就会自动显示出来)。

这里我们就可以看到有一个芯片,也就是我们生成的sof文件,只需要把这个文件烧录到你的开发板就行了。(注意:上面如果显示No Hardware的话,要点开旁边的接口设置,设置为USB接口就行了,连接了开发板就会自动显示出来)。

以上就是本期的全部内容了,我们下一次见!

分享一张壁纸: