滨州建设厅网站产品如何在网上推广

背景介绍

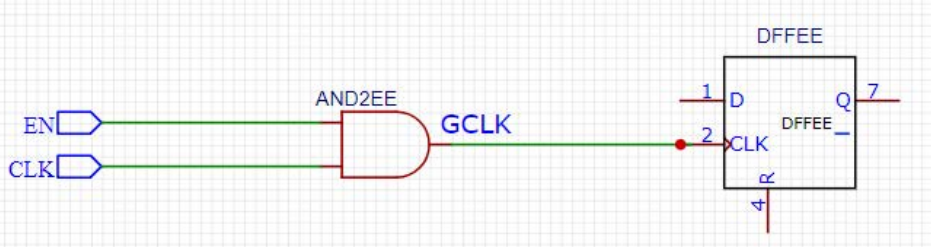

芯片功耗组成中,有高达 40%甚至更多是由时钟树消耗掉的。这个结果的原因也很直观,因 为这些时钟树在系统中具有最高的切换频率,而且有很多时钟 buffer,而且为了最小化时钟 延时,它们通常具有很高的驱动强度。 那么减少时钟网络的功耗消耗,最直接的办法就是如果不需要时钟的时候,就把时钟关掉。 这种方法就是大家熟悉的门控时钟:clock gating。 如果让我们设计一个门控时钟的电路,我们会怎么设计呢?最直接的方法,不需要时钟的时 候关掉时钟,这就是与操作,我们只需要把 enable 和 CLK 进行“与”操作不就行了么,电路 图如下 :

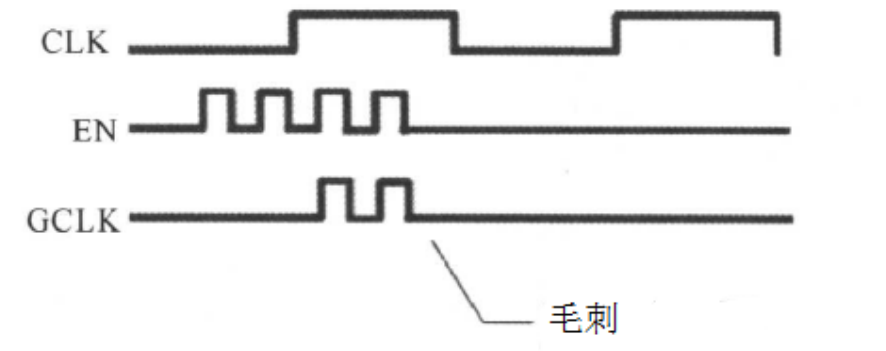

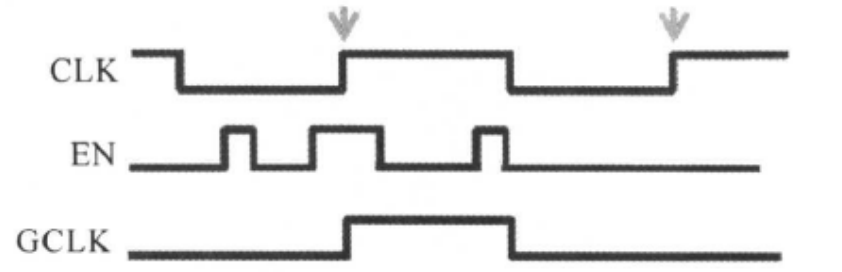

这种直接将控制 EN 信号和时钟 CLK 进行与操作完成门控的方式,可以完成 EN 为 0 时,时 钟被关掉。但是同时带来另外一个很大的问题:毛刺

如上图所示,EN 是不受控制的,随时可能跳变,这样纯组合输出 GCLK 就完全可能会有毛刺产生,时钟信号上产生毛刺是很危险的。

很自然的我们会想到解决方法,用触发器,只要把 EN 用 CLK 寄存一下,那么输出就是以 CLK 为基准了。其实还有一种办法是锁存器,把 EN 用锁存器锁存的输出,也是以 CLK 为基准的。

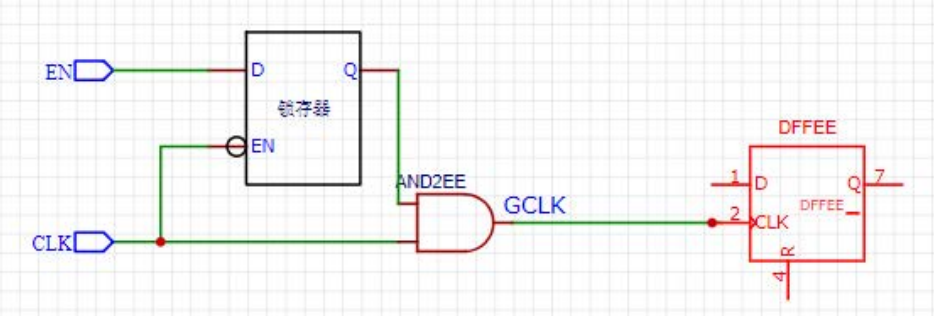

锁存门控

先来谈第二种方法,利用锁存器做clock gating,电路如下:

波形如下:

可以看到,只有在 CLK 为高的时候,GCLK 才可能会输出高,这样就能消除 EN 带来的毛刺。 这是因为 D 锁存器是电平触发,在 clk=1 时,数据通过 D 锁存器流到了 Q;在 Clk=0 时, Q 保持原来的值不变。

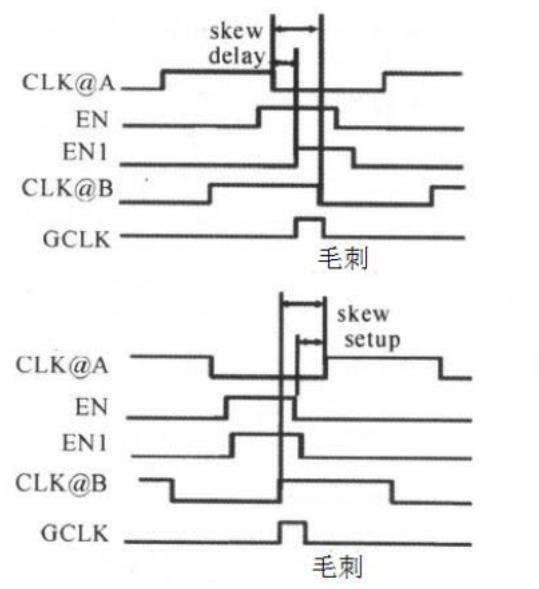

虽然达到了我们消除毛刺的目的,但是这个电路还有两个缺点: 1 如果在电路中,锁存器与与门相隔很远,到达锁存器的时钟与到达与门的时钟有较大的延 迟差别,则仍会出现毛刺。 2 如果在电路中,时钟使能信号距离锁存器很近,可能会不满足锁存器的建立时间,会造成 锁存器输出出现亚稳态。

上述的右上图中,B 点的时钟比 A 时钟迟到,并且 Skew > delay,这种情况下,产生了毛刺。 为了消除毛刺,要控制 Clock Skew,使它满足 Skew >Latch delay(也就是锁存器的 clk-q 的 延时)。上述的右下图中,B 点的时钟比 A 时钟早到,并且|Skew| > ENsetup 一 (D->Q),这 种情况下,也产生了毛刺。为了消除毛刺,要控制 Clock Skew,使它满足|Skew|< ENsetup 一(D->Q)。

寄存门控

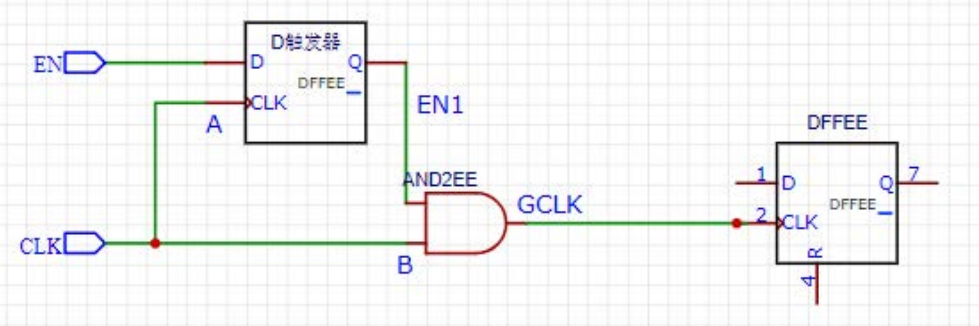

对于clock gating,我们还有另外的解决办法,就是用寄存器来寄存 EN 信号再与上 CLK 得到 GCLK,电路图如下所示:

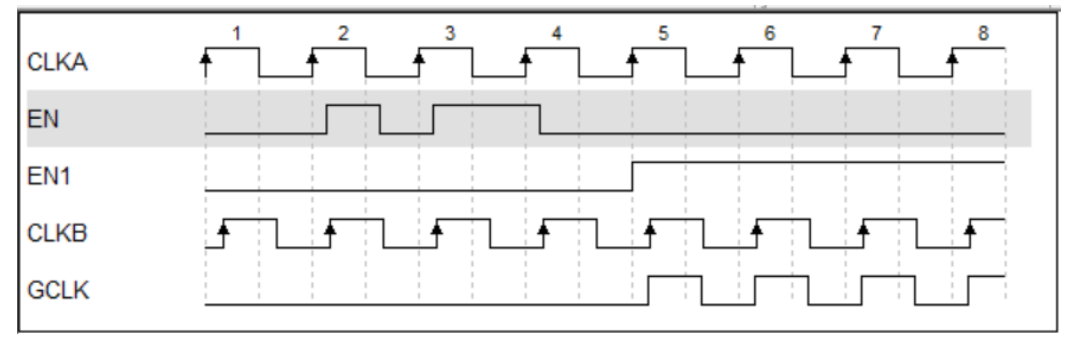

时序图如下所示:

由于 DFF 输出会 delay 一个周期,所以除非 CLKB 上升沿提前 CLKA 很多,快半个周期,才 会出现毛刺,而这种情况一般很难发生。但是,这种情况 CLKB 比 CLKA 迟到,是不会出现毛刺的。 当然,如果第一个 D 触发器不能满足 setup 时间,还是有可能产生亚稳态。

提问:SOC 芯片设计中使用最多的是锁存结构的门控时钟,为什么? 原因是:在实际的 SOC 芯片中,要使用大量的门控时钟单元。所以通常会把门控时钟做出一 个标准单元,有工艺厂商提供。那么锁存器结构中线延时带来的问题就不存在了,因为是做成一个单元,线延时是可控和不变的。而且也可以通过挑选锁存器和增加延时,总是能满足 锁存器的建立时间,这样通过工艺厂预先把门控时钟做出标准单元,这些问题都解决了。

那么用寄存器结构也可以达到这种效果,为什么不用寄存器结构呢?那是因为面积!一个 DFF 是由两个 D 锁存器组成的,采样 D 锁存器组成门控时钟单元,可以节省一个锁存器的 面积。当大量的门控时钟插入到 SOC 芯片中时,这个节省的面积就相当可观了

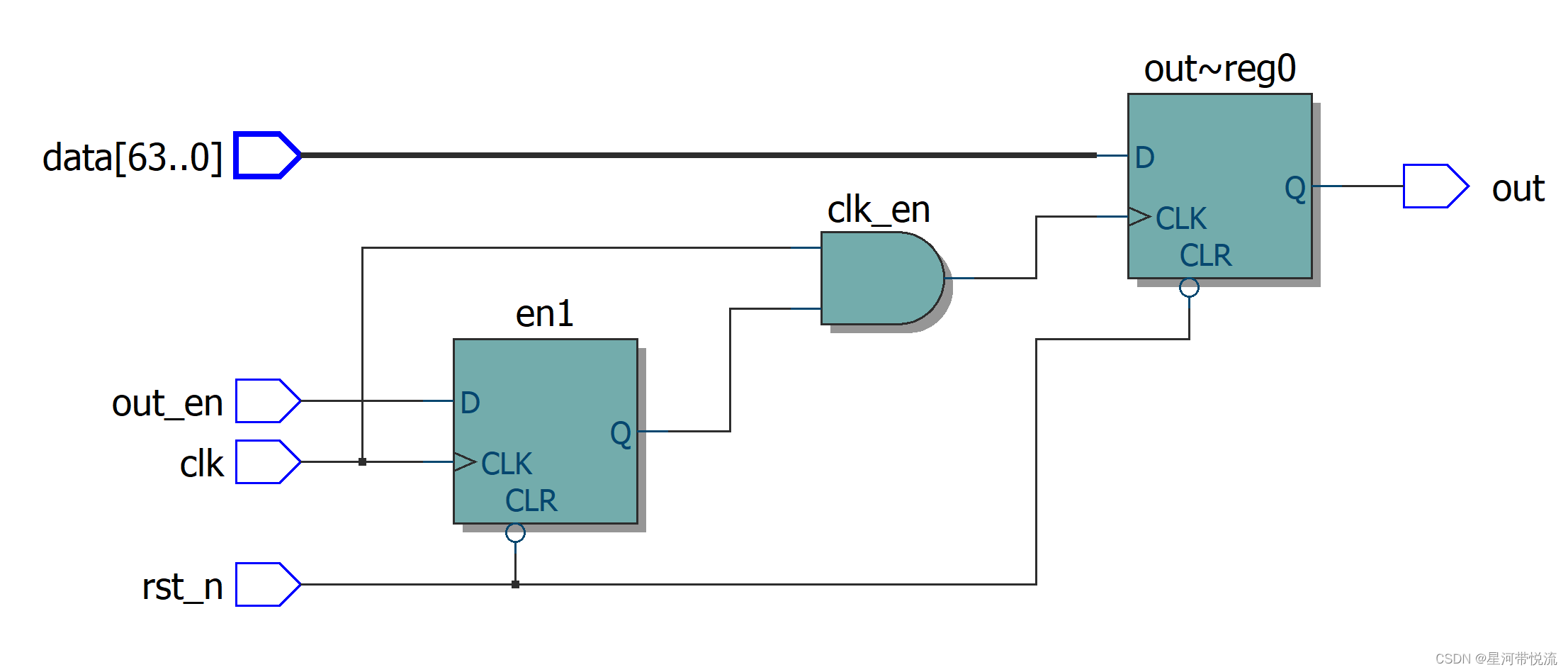

代码(寄存器门控)

module clk_gating(input clk ,input rst_n , input out_en ,input [63:0] data ,output reg out

);reg en1;

wire clk_en;always@(posedge clk or negedge rst_n) beginif(!rst_n)beginen1 <= 1'b0;endelse beginen1 <= out_en;end

end

assign clk_en = clk & en1;

always @(posedge clk_en or negedge rst_n) beginif(rst_n==1'b0)out <= 64'b0;elseout<= data;

end

endmodule综合出来电路如下,和我们预想的一样。